AMD next-gen socket SP7 reportedly launches alongside Venice data-center CPUs

The upcoming AMD EPYC processor codenamed “Venice,” that includes Zen6 CPU cores, is alleged to be appropriate with a brand new SP7 socket.

Within the upcoming months, we will anticipate to listen to extra about merchandise akin to Intel Xeon Falcon Shore, NVIDIA Blackwell, and AMD EPYC Venice. These codenames characterize the potential lineup for the 2025 data-center collection, which is able to embody a spread of combos involving CPUs, GPUs, and XPUs, relying on how the corporate chooses to call them.

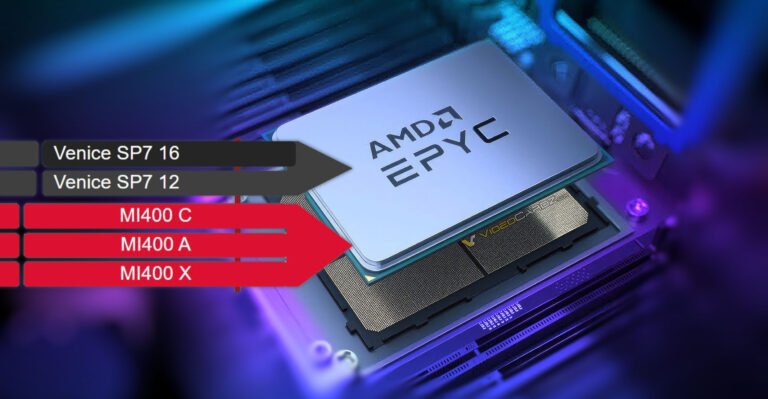

A current roadmap shared by YuuKi has revealed AMD’s plans to unveil a recent collection of Intuition MI400 merchandise, comprising C, A, and X variants, along with their new EPYC Venice processor collection. Curiously, if this roadmap seems to be correct, it means that the Venice processor would require a brand new socket often known as SP7.

Information-Heart Roadmap for 2025, Supply: YuuKi-AnS

Moreover, it seems that this collection will help 12-channel and 16-channel DDR5 reminiscence configurations, representing an improve from the present collection, which helps as much as 12 channels. When it comes to rumors, there may be hypothesis that the Zen6-based Venice product household would possibly doubtlessly develop into the primary AMD structure to interrupt the 384-core rely on a single package deal. Nonetheless, it’s essential to notice that this rumor has not been formally confirmed as of but.

The AMD Venice collection is anticipated to comply with the EPYC Turin collection, which options the Zen5 structure and is reportedly appropriate with the SP5 and SP6 sockets at present utilized by EPYC Genoa and Bergamo, that includes Zen4 CPU cores. Not like the plans laid out for Zen4 and Zen5, AMD has not but disclosed particular particulars in regards to the Zen6 EPYC collection, aside from confirming its existence on the leaked roadmap.

The introduction of a brand new socket implies that the Zen6 structure will probably be packaged in a different way, probably to accommodate extra chiplets, which may very well be a strategic transfer to handle Intel’s growing CPU sizes within the data-center market. Superior packaging methods are anticipated to play a major position in future CPU architectures, as firms discover stacking compute chiplets on high of one another to reinforce efficiency and effectivity.

AMD EPYC Venice CPUs shouldn’t be anticipated ahead of 2025. The corporate is but to launch its EPYC 8004 Siena structure specializing in telecommunication techniques and servers on the sting. These collection are mentioned to make the most of smaller SP6 socket with decreased reminiscence help to eight channels.

| AMD EPYC Processor Sequence | ||||

|---|---|---|---|---|

| VideoCardz | Zen3 | Zen4 | Zen5 | Zen6 |

| Codename | 7003 “Milan(-X)” | 9004 “Genoa(-X)” 8004 “Bergamo” * 8004 “Siena” |

9005 “Turin(-X)” 8005 “Turin-Dense” * |

9006 “Venice” |

| Launch | 2021 | 2023 | 2024+ | 2025+ |

| Socket | SP3 (LGA4094) | SP5 (LGA-6096) SP6 (LGA 4094) |

SP5 (LGA-6096) SP6 (LGA 4094) |

SP7 |

| Max Cores | TBC | |||

| Max Mem. Channels | ||||

Supply: YuuKi_AnS