The trendy world actually runs on electrical motors. They’re utilized in each side of producing, logistics, and transportation. Again within the earliest days of electrical motors, when motors had been nonetheless fairly huge and costly, a motor’s mechanical output energy would seemingly be distributed to particular person workstations inside a manufacturing facility by way of a system of belts, pulleys, and drive shafts. Many late 18th and early 19th century factories already had these mechanical drive programs in place to distribute steam or water-wheel energy, so it made sense to easily exchange these older energy sources utilizing an electrical motor to drive the prevailing mechanical power-distribution system immediately. Nonetheless, as the price and measurement of electrical motors decreased, it quickly made extra sense to construct electrical motors immediately into the gadgets they powered. Electrical motors shortly grew to become ubiquitous.

Immediately, in line with an Worldwide Power Company report titled Power Effectivity 2022“Electrical motors and motor-driven programs account for round 70% of the whole world electrical use of the commercial sector.” Consequently, it is smart each economically and environmentally to drive these electrical motors as effectively as potential.

Environment friendly motor management has lengthy been a goal software for FPGAs due to the real-time nature of motor management and since there are various varieties of electrical motors of various sizes, from fractional-horsepower motors to massive electrical motors that drive ships and locomotives, and there are alternative ways of driving these motors relying on their kind, measurement, and software. With so many assorted motor-control algorithms, it’s very exhausting to develop a one-size-fits-all motor-control IC, which is why versatile, programmable FPGAs match so nicely with this form of management software.

AMD has now focused motor-control purposes immediately with the latest member of the Kria SoM (System on Module) household. The Kria K24 SoM relies on a singular Zynq UltraScale+ MPSoC developed particularly for this motor-control SoM. Bodily, the Kria K24 SoM is about half the dimensions of a bank card, so it’s simple to design the SoM into an finish product, and that’s exactly how AMD expects to see it used. Single unit pricing is $250 for a commercial-grade Kria K24 SoM and $350 for an industrial-grade Kria K24 SoM. Together with the K24 SoM, AMD has additionally developed the $399 KD240 Drives Starter Package, proven beneath in Determine 1. The corporate has added accelerated motor management libraries to the Vitis improvement atmosphere and created improvement flows for motor-control purposes utilizing Python and MATLAB’s Simulink to assist in creating purposes for this SoM.

Determine 1: AMD KD240 Drives Starter Package for motor-control purposes, together with a Kria K24 SoM below the warmth sink. Picture credit score: AMD

The Zynq UltraScale+ MPSoC developed particularly for the Kria K24 SoM incorporates a quad-core Arm Cortex-A53 software processor and a dual-core Arm Cortex-R5F real-time processor, 154K “system logic cells” (the strategy that AMD makes use of to measure programmable-logic capability for UltraScale and UltraScale+ FPGA materials), and 132 I/O pins that can be utilized for connecting motors, sensors, and different subsystems. The Kria K24 SoM contains 2 Gbytes of 32-bit LPDDR4 SDRAM, and it has 4 USB ports and 4 gigabit Ethernet ports with TSN (time-sensitive networking) capabilities. TSN is used to implement real-time, deterministic Ethernet networks, that are more and more required in industrial community environments. The TSN capabilities require utilizing a number of the MPSoC’s on-chip programmable logic to implement the required real-time {hardware}.

The Kria K24 SoM libraries embody help for a number of varieties of motors, together with induction motors, brushed and brushless permanent-magnet motors, reluctance motors, and servo motors. The library accommodates greater than 25 accelerated and demonstration purposes for the Kria K24 SoM and builds on the prevailing firm’s current Vitis Motor Management library. Per AMD, the next Vitis Imaginative and prescient Library APIs are leveraged closely:

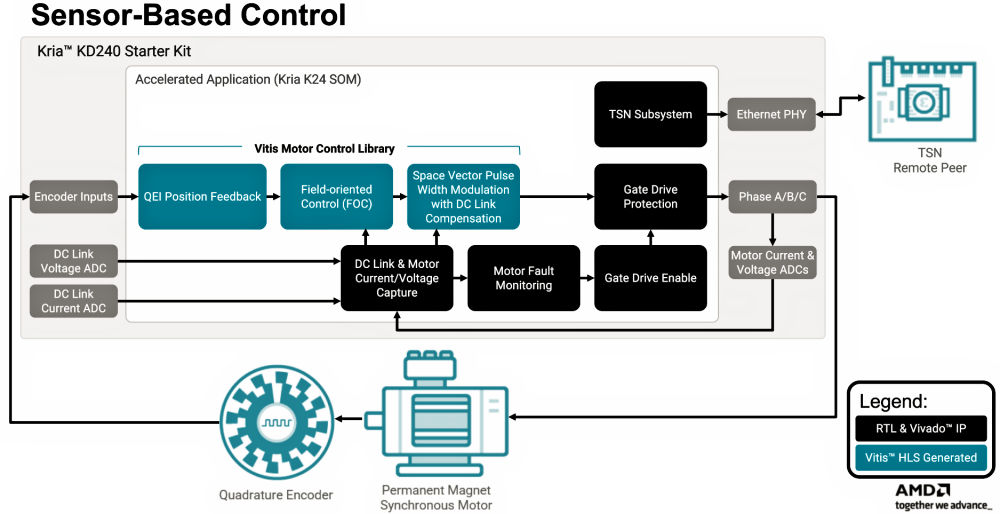

- FOC (Discipline-Oriented Management): Sensor-based FOC with eight management modes masking fundamental pace and torque management modes.

- SVPWM_DUTY: The entrance finish for Area Vector Pulse Width Modulation (SVPWM). Used to calculate duty-cycle ratios.

- PWM_GEN: The SVPWM again finish, which generates output alerts based mostly on duty-cycle ratios calculated by SVPWM_DUTY.

- QEI: Quadrature encoder interface.

AMD provided a graphic (see Determine 2) displaying how the assorted Kria KD240 library modules work collectively to create a sensor-based motor-control subsystem.

Determine 2: Block diagram of a motor-control subsystem based mostly on the Kria KD240 Drives Starter Package libraries. Picture credit score: AMD

The Kria K24 SoM additionally helps AMD’s Deep-learning Processor Unit (DPU), a soft-core IP block that the corporate developed particularly for its household of Zynq UltraScale+ MPSoCs. This DPU is a configurable computation engine optimized for convolutional neural networks. (Observe: This use of the three-letter abbreviation “DPU” doesn’t correspond in any solution to the predominant use of the time period, which refers to a data-processing unit designed for use in high-speed networking purposes.) This AMD DPU is a microcoded compute engine constructed from the MPSoC’s programmable logic that helps the AI inference wants of convolutional neural networks. As such, this DPU for the MPSoC can be utilized so as to add AI inference capabilities to the motor-control algorithms carried out with the Kria K24 SoM. The library for the KR24 SoM features a DPU-PYNQ software, which brings AMD’s PYNQ Python programming and Jupyter Pocket book environments for embedded programs to the KR24 SoM.

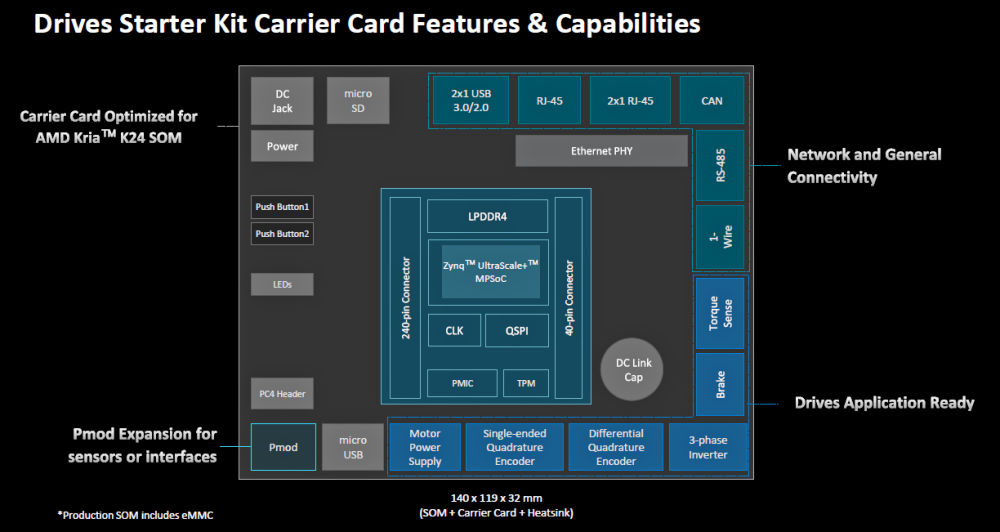

Determine 3 exhibits a block diagram of the KD240 Drives Starter Package, which consists of the Kria K24 SoM and a specialised motor-control service card.

Determine 3: Block Diagram of the AMD KD240 Drives Starter Package for motor-control purposes, together with the Kria K24 SoM, proven within the heart of the board. Picture credit score: AMD

As Determine 3 illustrates, the KD240 Drives Starter Package service card contains a number of interface ports that could be wanted in a robotic or different motor-control software, together with two common USB ports and a microUSB port, three Ethernet ports, a CAN bus interface, and an RS-485 interface. Interfaces for sensors usually related to motor management embody single-ended and differential quadrature encoder interfaces and a torque-sensor interface.

AMD additionally has plans for 2 motor accent packs to enhance the KD240 Drives Starter Package. The primary such pack, obtainable now, is the AMD Kria KD240 Motor Accent Pack, which features a brushless DC motor meeting with a built-in quadrature encoder from Anaheim Automation and Discipline-Oriented Management (FOC) purposes for controlling the motor. This accent pack is designed to make it simple to develop preliminary motor-control purposes with the KD240 Drives Starter Package. The accent second pack, quickly to be launched, is the REV Robotics 2-in-1 Motor Package Accent, which features a REV Robotics brushless DC motor, a ball-shooter meeting (primarily a motor-controlled throwing arm), a easy robotic arm meeting, and an accelerated, sensorless FOC software for controlling the motor. This second accent pack is clearly aimed on the varied robotic competitions by which REV Robotics participates and provides components and knowhow.

Observe: Should you’d like to know how AMD’s “system logic cells” for UltraScale and UltraScale+ FPGAs differ from plain previous “logic cells,” Michael Posner wrote a pleasant clarification in a Synopsys weblog titled “Understanding Xilinx System Logic Cells vs. Logic Cells” method again in 2015.

Associated