Intel is working by itself model of steady cache that AMD pioneered with its 3D V-Cache know-how, although it’s nonetheless at the very least a few generations away.

Following Intel CEO Pat Gelsinger’s Intel Innovation 2023 keynote, Gelsinger held a Q+A session with members of the press the place he was requested if Intel would undertake the identical stackable cache know-how that AMD has been utilizing to make a few of the greatest processors in the marketplace.

“While you reference V-Cache,” Gelsinger stated, as reported by Tom’s {Hardware}, “you are speaking a few very particular know-how that TSMC does with a few of its clients as effectively. Clearly, we’re doing that in a different way in our composition, proper? And that individual kind of know-how is not one thing that is a part of [the new Intel Core Ultra processors]however in our roadmap, you are seeing the thought of 3D silicon the place we’ll have cache on one die, and we’ll have CPU compute on the stacked die on high of it, and clearly utilizing [embedded multi-die interconnect bridges] that Foveros [chiplet packaging technology] we’ll have the ability to compose completely different capabilities.”

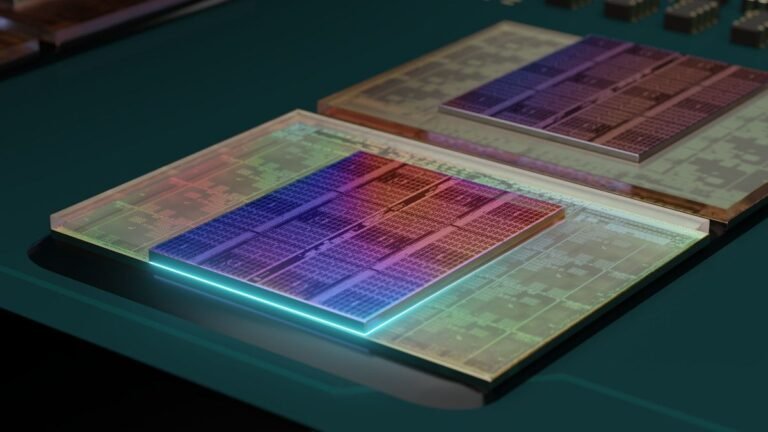

Anybody who noticed Gelsinger’s keynote would have seen how Intel’s upcoming processor roadmap will transfer closely into the multi-chiplet module (MCM) design paradigm, the place completely different processor elements just like the iGPU, cache, and Intel’s new nueral processing unit could be discrete segments bonded collectively right into a single unit quite than forged collectively unexpectedly.

The MCM course of permits for lots extra flexibility than the extra restrictive monolithic silicon fabrication that has historically been used beforehand, and would clearly open up all types of recent prospects for chip design that weren’t sensible utilizing a monolithic construction.

The obvious of those is stacked cache, which enormously will increase the out there cache reminiscence pool for the processor that interprets into a lot sooner processing of particular CPU workloads.

AMD has already confirmed the advantages of this expanded cache pool when it launched the AMD Ryzen 7 5800X3D chip in 2022, adopted by AMD Ryzen 7 7800X3D, AMD Ryzen 9 7900X3D, and AMD Ryzen 9 7950X3D earlier this yr.

“We really feel excellent that we’ve superior capabilities for next-generation reminiscence architectures, benefits for 3D stacking, for each little die, in addition to for very massive packages for AI and high-performance servers as effectively,” Gelsinger stated. “So we’ve a full breadth of these applied sciences. We’ll be utilizing these for our merchandise, in addition to presenting it to the [Intel] Foundry clients as effectively.”

Stackable cache is just the start for Intel’s packaging tech

Intel’s transfer into MCM processor design utilizing its embedded multi-die interconnect bridge (EMIB) and Forveros chip packaging know-how is a serious step ahead for the chipmaker.

The perfect Intel processors of the previous couple of years have relied closely on merely throwing uncooked electrical energy into its processors to extend efficiency, making its high-end Intel Core i9-12900K and Intel Core i9-13900K particularly energy hungry processors.

This has allowed it to regain loads of floor misplaced to the most effective AMD processors of the previous few years, however this is not a workable long run resolution, and even Nvidia is reportedly seeing the knowledge of transferring to an MCM design for its next-gen Nvidia Blackwell structure.

And whereas the thought of a future Intel processor, probably as quickly as Lunar Lake, that includes stacked cache is thrilling, it ought to solely be the start of recent processor developments, not the tip of it.