AMD’s Ryzen X3D V-Cache processors are the quickest gaming chips available on the market, with as much as 144MB of on-die cache. Courtesy of the vertically stacked SRAM, Staff Purple has delivered a number of era upgrades inside a single cycle. Until now, enhance clock hikes have been Intel’s main response to the Ryzen V-Cache menace. Along with Samsungit’s lastly engaged on a worthy competitor to the 3D-stacked CPUs from its archrival.

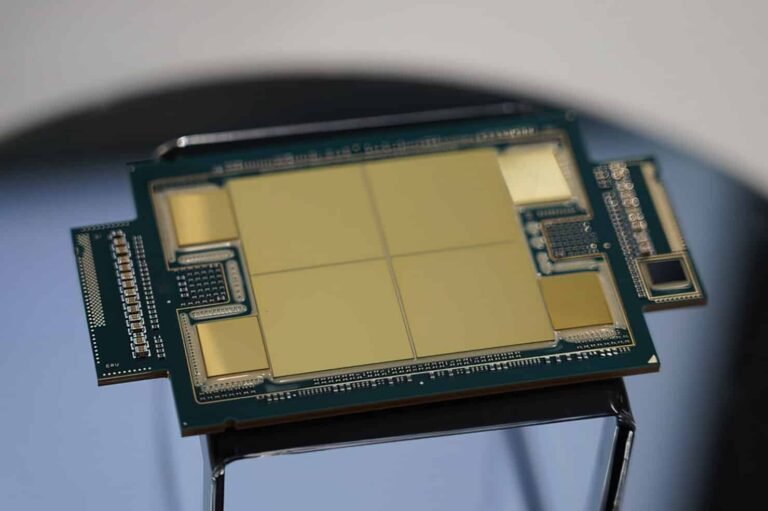

Samsung is growing its next-gen “cache DRAM” know-how that will finally change the expensive HBM chips. An HBM bundle consists of a number of DRAM dies stacked vertically on prime of each other, with the bottom die linked to the first CPU or GPU die. HBM is thought for being energy environment friendly with low voltages and a large bus. Traditionally, it has been used on GPUs, most notably information middle accelerators such because the A100 and H100.

Cache DRAM makes use of a single chip with the capability of a number of HBM dies 3D stacked instantly atop the CPU or GPU compute die. Storing the mandatory information nearer to the processing items drastically reduces latency and effectivity. Samsung claims that cache DRAM reduces energy consumption by 60% whereas boosting information switch by 50% over present HBM options. At the moment, the dissipation of the warmth generated by the 3D-stacked DRAM is the first concern.

TSMC was in a position to signal a number of long-term contracts with NVIDIA and AMD because of its superior 3D packaging applied sciences, CoWoS and SoIC. Regardless of having only a few severe purchasers, CoWoS packaging capability is absolutely utilized for the foreseeable future. NVIDIA’s Tensor core GPUs, alongside the Epyc Milan and Genoa-X CPUs (and shortly the MI300), are tanking TSMC’s capability.

Intel has teamed up with Samsung to use cache DRAM to its processors and also will undertake it inside its foundry, providing it to 3rd events. Samsung has two 2.5D packaging applied sciences, H-Dice and I-Dice, much like TSMC’s FOWLP 2.5D answer. Nonetheless, the cache DRAM possibility will leverage X-Dice 3D stacking, bolstered by an Intel collaboration, to scale back prices and broaden capability.

Mass manufacturing of cache DRAM-powered chips is anticipated to start in 2025with Intel manufacturing the primary processors. NVIDIA has additionally proven curiosity within the know-how and hopes to combine it into its information middle merchandise.

Supply: Naver (Through: Revengus).