The studies about an inadequate provide of compute GPUs used for synthetic intelligence (AI) and high-performance computing (HPC) servers turned frequent in current months as demand for GPUs to energy generative AI purposes exploded. TSMC admits that the largest compute GPU provide bottleneck is its CoWoS packaging capability, as it’s utilized by nearly everybody within the AI and HPC enterprise. The corporate is increasing CoWoS capability however believes that its scarcity will persist for 1.5 years.

“It will not be the scarcity of AI chips,” stated Mark Liu, the chairman of TSMC, in a dialog with Nikkei. “It is the scarcity of our CoWoS capability. […] At present, we can not fulfill 100% of our clients’ wants, however we attempt to assist about 80%. We expect this can be a momentary phenomenon. After our enlargement of [advanced chip packaging capacity]it needs to be alleviated in a single and a half years.“

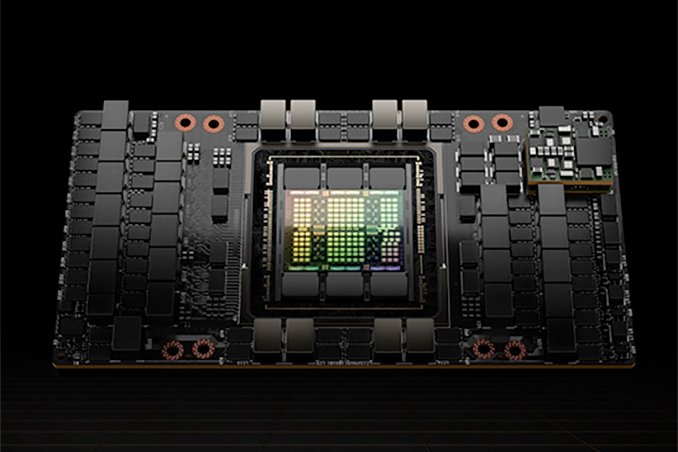

TSMC at the moment produces the overwhelming majority of processors that energy fashionable AI providers, together with compute GPUs (akin to AMD’s Intuition MI250 and NVIDIA’s A100 and H100), FPGAs, and specialised ASICs from firms like d-Matrix and Tenstorrent in addition to proprietary processors from cloud service suppliers, akin to AWS’s Trainium and Inferentia in addition to Google’s TPU.

It’s noteworthy that compute GPUs, FPGAs, and accelerators from CSPs all use HBM reminiscence to get the best bandwidth doable and use TSMC’s interposer-based chip-on-wafer-on-substrate packaging. Whereas conventional outsourced semiconductor meeting and check (OSAT) firms like ASE and Amkor additionally provide comparable packaging applied sciences, it seems like TSMC is getting the lion’s share of the orders, which is why it could actually barely meet demand for its packaging providers.

Business analysts consider that OSATs are much less motivated to supply superior packaging providers as a result of it requires them to take a position hefty quantities of capital and poses extra monetary dangers than conventional packaging. For instance, if one thing goes incorrect with a mainstream processor that sits on an natural substrate, an OSAT loses just one chip, whereas if one thing goes incorrect with a bundle carrying 4 chiplets and eight HBM reminiscence stacks, the corporate loses tons of if not hundreds of {dollars}. Since OSATs don’t get substantial margins making these chiplets, such dangers decelerate the enlargement of superior packaging capability at OSATs, though superior packaging prices considerably more cash than conventional packaging.

Similar to its trade friends, TSMC is spending billions on upcoming superior packaging amenities. For instance, the corporate just lately introduced plans to spend practically $2.9 billion on a packaging fab that’s rumored to come back on-line in 2027.

“We’re growing our capability as rapidly as doable,” stated C.C. Wei, chief government of TSMC, on the firm’s earnings name earlier this 12 months. “We anticipate these tightness considerably be launched in subsequent 12 months, in all probability in direction of the tip of subsequent 12 months. […] I cannot provide the precise quantity [in terms of processed wafers capacity]however CoWoS [capacity will be doubled in 2024 vs. 2023].“

Supply: Nikkei